Q-Tech CRYSTAL時鐘終端技術(shù)和負(fù)載匹配說明

來源:http://eitherspanlaw.com 作者:億金電子 2019年01月25

Q-Tech Corporation成立于1972年,旨在為高要求產(chǎn)品應(yīng)用的公司提供最先進的石英晶振,SMD晶振,時鐘振蕩器和頻率控制解決方案.Q-Tech CRYSTAL公司的理念是,采用先進的振蕩器技術(shù)制造的產(chǎn)品,致力于質(zhì)量,準(zhǔn)時交貨和客戶服務(wù),將為我們的客戶及其需求帶來巨大的利益.下面要給大家介紹到的是Q-Tech CRYSTAL時鐘終端技術(shù)和負(fù)載匹配說明.

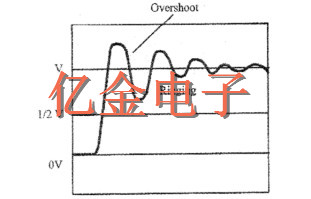

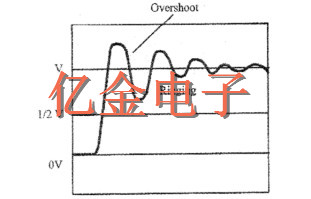

由于ACMOS和低阻抗輸出的快速轉(zhuǎn)換,正確當(dāng)設(shè)備用于驅(qū)動負(fù)載時,必須使用終端技術(shù)大阻抗導(dǎo)致阻抗不匹配.端接通常用于解決電壓反射問題實質(zhì)上導(dǎo)致時鐘波形中的步驟以及過沖和下沖.

這種影響可能導(dǎo)致數(shù)據(jù)的錯誤時鐘,以及更高的EMI和系統(tǒng)噪聲.由于PCB走線的長度和負(fù)載,也需要端接組態(tài).有三種終止時鐘跟蹤的通用方法,這是一個過程將器件的輸出阻抗與線路阻抗相匹配:系列終端,上拉/下拉終端,并聯(lián)AC終端

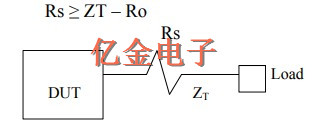

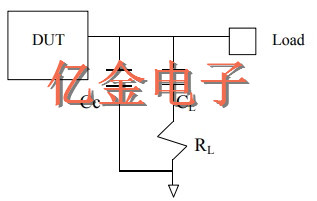

方法1:系列終止

在串聯(lián)終端中,阻尼電阻靠近時鐘源(Q-Tech晶振)放置信號. Rs的值必須滿足以下要求: 大多數(shù)Q-Tech晶體振蕩器都有一個內(nèi)置串聯(lián)電阻,其典型值介于兩者之間10Ω和50Ω. 如果需要額外的電阻,則應(yīng)將電阻放置為盡可能接近時鐘源.大值電阻可能會增加上升和下降時間和負(fù)載和頻率有關(guān).

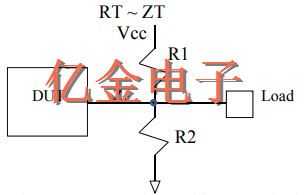

方法2:上拉/下拉終止

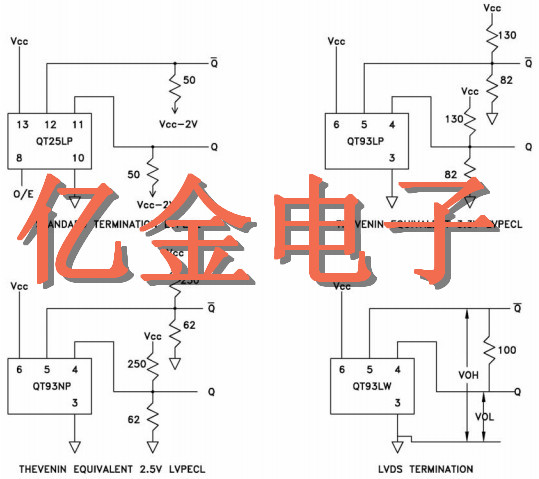

在上拉/下拉終止中,戴維寧相當(dāng)于組合等于跡線的特征阻抗.這可能是最干凈的導(dǎo)致沒有反射和EMI.

戴維寧終端最常用于負(fù)載的PECL邏輯阻抗為50Ω.

戴維寧終端最常用于負(fù)載的PECL邏輯阻抗為50Ω.

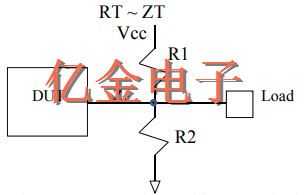

方法3:并行終止

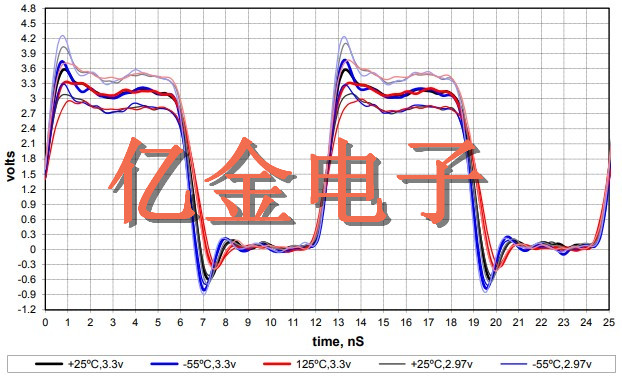

在并聯(lián)終端中,R-C組合放置在負(fù)載處的價值必須仔細(xì)選擇電容,通常小于50pF.這種終止是不推薦,因為它會降低時鐘的上升和下降時間,雖然它沒有吸收直流電流. QT625L NCS AC00 SN 8238 80 MHZ

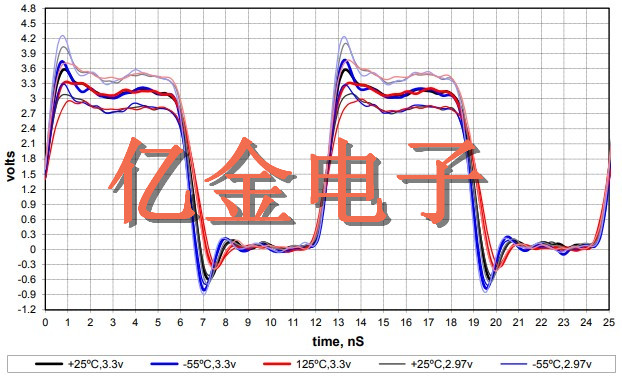

Agilent DSO6104A 2pf 800Mhz探頭,(總負(fù)載10pF)

1uF||0.1uF extl旁路

LVPECL和LVDS

LVPECL和LVDS

差分晶振的LVPECL和LVDS邏輯輸出提供了優(yōu)于HCMOS石英晶體振蕩器和TTL技術(shù)具有低成本,高速快速上升和下降時間,低功耗和低功耗,低抖動.LVDS差分晶振具有最低的差分?jǐn)[幅和典型電壓

擺幅為350mV,典型偏移電壓為1.25V. PCB的關(guān)鍵指南

-RF信號對噪聲非常敏感.招致的可能性必須小心對待振鈴和反射.

-阻抗匹配對RF至關(guān)重要.PCB設(shè)計師必須考慮保持線路阻抗50Ω;驅(qū)動器輸出50Ω,50Ω在傳輸過程中,50Ω進入接收器.

-必須盡量減少回?fù)p.這種損失是由信號反射引起的,或響.返回是返回電流所采用的路徑.

由傳輸線上的Q-Tech晶振阻抗不匹配產(chǎn)生的振鈴

由傳輸線上的Q-Tech晶振阻抗不匹配產(chǎn)生的振鈴

-在Vcc和地之間添加去耦電容,并將它們放置在接地附近時鐘振蕩器的Vcc功率.需要去耦電容

減少可能傳輸?shù)綍r鐘信號的噪聲.

-記住串?dāng)_因素.作為系統(tǒng)性能和板密度增加,串?dāng)_的問題以及如何處理它變成了更重要.串?dāng)_是相鄰之間的能量轉(zhuǎn)移,導(dǎo)體由于互感和并聯(lián)電容.

-同時保持信號走線盡可能遠.

-線與eah其他線平行的距離應(yīng)保持為a最小.

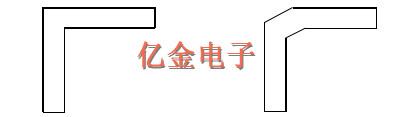

-避免在軌跡上形成90°直角彎曲.盡量保持直線,除非必要的或保持45°切割痕跡.

由于ACMOS和低阻抗輸出的快速轉(zhuǎn)換,正確當(dāng)設(shè)備用于驅(qū)動負(fù)載時,必須使用終端技術(shù)大阻抗導(dǎo)致阻抗不匹配.端接通常用于解決電壓反射問題實質(zhì)上導(dǎo)致時鐘波形中的步驟以及過沖和下沖.

這種影響可能導(dǎo)致數(shù)據(jù)的錯誤時鐘,以及更高的EMI和系統(tǒng)噪聲.由于PCB走線的長度和負(fù)載,也需要端接組態(tài).有三種終止時鐘跟蹤的通用方法,這是一個過程將器件的輸出阻抗與線路阻抗相匹配:系列終端,上拉/下拉終端,并聯(lián)AC終端

方法1:系列終止

在串聯(lián)終端中,阻尼電阻靠近時鐘源(Q-Tech晶振)放置信號. Rs的值必須滿足以下要求: 大多數(shù)Q-Tech晶體振蕩器都有一個內(nèi)置串聯(lián)電阻,其典型值介于兩者之間10Ω和50Ω. 如果需要額外的電阻,則應(yīng)將電阻放置為盡可能接近時鐘源.大值電阻可能會增加上升和下降時間和負(fù)載和頻率有關(guān).

方法2:上拉/下拉終止

在上拉/下拉終止中,戴維寧相當(dāng)于組合等于跡線的特征阻抗.這可能是最干凈的導(dǎo)致沒有反射和EMI.

方法3:并行終止

在并聯(lián)終端中,R-C組合放置在負(fù)載處的價值必須仔細(xì)選擇電容,通常小于50pF.這種終止是不推薦,因為它會降低時鐘的上升和下降時間,雖然它沒有吸收直流電流. QT625L NCS AC00 SN 8238 80 MHZ

Agilent DSO6104A 2pf 800Mhz探頭,(總負(fù)載10pF)

1uF||0.1uF extl旁路

差分晶振的LVPECL和LVDS邏輯輸出提供了優(yōu)于HCMOS石英晶體振蕩器和TTL技術(shù)具有低成本,高速快速上升和下降時間,低功耗和低功耗,低抖動.LVDS差分晶振具有最低的差分?jǐn)[幅和典型電壓

擺幅為350mV,典型偏移電壓為1.25V. PCB的關(guān)鍵指南

-RF信號對噪聲非常敏感.招致的可能性必須小心對待振鈴和反射.

-阻抗匹配對RF至關(guān)重要.PCB設(shè)計師必須考慮保持線路阻抗50Ω;驅(qū)動器輸出50Ω,50Ω在傳輸過程中,50Ω進入接收器.

-必須盡量減少回?fù)p.這種損失是由信號反射引起的,或響.返回是返回電流所采用的路徑.

-在Vcc和地之間添加去耦電容,并將它們放置在接地附近時鐘振蕩器的Vcc功率.需要去耦電容

減少可能傳輸?shù)綍r鐘信號的噪聲.

-記住串?dāng)_因素.作為系統(tǒng)性能和板密度增加,串?dāng)_的問題以及如何處理它變成了更重要.串?dāng)_是相鄰之間的能量轉(zhuǎn)移,導(dǎo)體由于互感和并聯(lián)電容.

-同時保持信號走線盡可能遠.

-線與eah其他線平行的距離應(yīng)保持為a最小.

-避免在軌跡上形成90°直角彎曲.盡量保持直線,除非必要的或保持45°切割痕跡.

避免90°直角彎曲 使用45°角度彎曲

-差分晶振輸出LVDS或LVPECL的Q和QNOT之間的差分走線應(yīng)該是長度相等以避免阻抗不匹配和不同的傳播延遲時間.

正在載入評論數(shù)據(jù)...

相關(guān)資訊

- [2024-11-09]溫度補償晶體振蕩器 JT21LE,功耗極低...

- [2023-06-26]Rakon推出RakonXpress品牌的現(xiàn)成頻率...

- [2023-06-20]Cardinal晶振公司環(huán)境政策,CSM1Z-A0B...

- [2023-06-20]Cardinal晶振ROSH證明,CX532Z-A2B3C5...

- [2023-06-17]為什么選擇ClearClock有源晶振,AK2AD...

- [2021-01-21]低功耗性能且含數(shù)字溫度補償?shù)臅r鐘IC...

- [2020-12-04]TXC晶振車規(guī)級頻率組件最新產(chǎn)品應(yīng)用方...

- [2020-10-19]石英振蕩器系列六——產(chǎn)品未來應(yīng)用市...

銷售代表

銷售代表